ARINC 429 IP Core for FPGA

BRM429D

Sital’s ARINC 429 IP Core for FPGA is fully compliant to the ARINC-429 standard. Sital can supply its ARINC-429 IP cores with up to 16 transmit channel and 16 receive channels, with data rate programmable for all channels (12.5 or 100 Kbps). By means of a proprietary technique, Sital can reduce the logic resource requirements by up to 70% for multi-channel ARINC-429 implementations.

Sital’s ARINC-429 architecture includes 32-bit wide, programmable-depth FIFOs with separate FIFOs for transmitting and receiving. Sital’s 429 decoders include a noise filtering mechanism to enhance receiver robustness. Sital’s 429 receive channel architecture also includes programmable address recognition, with 256 labels for each receive channel; and selection of either even, odd or no parity. Sital’s ARINC-429 IP is supplied as a single VHDL netlist of one or multiple transmit and/or receive channels, and includes a full verification environment.

In addition, Sital can supply ARINC-429 IP with DO-254 certifiability up to and including DAL A, along with VxWorks, Linux and Windows software drivers providing DO-178 certifiability up to and including DAL A. For the certifiable ARINC-429 IP and software, artifacts are available from a third-party company, Logicircuits.

Another capability that Sital can provide for ARINC-429 is its Safe and Secure (SnS) technology. By means of enhanced physical layer modeling, Sital’s SnS can detect cyber authentication violations. In addition, the SnS sensors can also detect and locate electrical faults such as intermittent or continuous open or short circuits in cables, connectors or LRUs.

Features

- ARINC 429 specification compatible

- Separated channels for ARINC 429 Data Transmit and Receive

- 32 bits wide, programmable depth, separated FIFO buffers for transmit and receive

- Provided with documentation to certify the design for DO-254 DAL-A

- Includes noise filtering mechanism to enhance receiver robustness

- Programmable data rate on each channel (12.5/100 Kbps)

- Programmable label recognition with 256 Labels for each Receiver

- Programmable parity: Even, Odd or No-parity (32nd bit as data)/li>

- FIFO full/empty indication

- Supports standard line drivers

- Multiple running clock options to reduce design time domains

- Small FPGA area utilization

- Modular architecture allowing flexible implementations. Any number of transmitters and receivers available in a single Netlist

- Provided with full verification environment

- Based on vendor and technology independent VHDL code

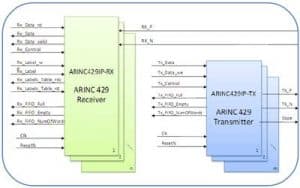

ARINC 429 Tx/Rx Core Operation

The ARINC429IP Core is divided between two independent modules for transmit (ARINC429IP-TX) and receive (ARINC429IP-RX).

A user can order any combination of transmitters and receivers which are packaged under the same FPGA netlist.

Each ARINC 429 channel (Rx / Tx) has 32 bits wide FIFO memory. (FIFO depth is selectable by the user).

ARINC 429 Transmitter

Whenever a data is written into to the Tx_FIFO, the ARINC429IP-TX Core will start transmitting this data to the serial Tx ports based on the Tx channel control register configuration. Data will be transmitted consequentially word after word until the Tx_FIFO will become empty.

Tx_FIFO status (Empty/Full) and Number_Of_Words are reported in the dedicated ports.

Once FIFO_Full is asserted, there is no option to write new words to the Tx_FIFO.

ARINC 429 Receiver

The ARINC429IP-RX Core receives data from the ARINC 429 bus and converts it to the local bus. This core performs serial-to-parallel conversion, gap/parity check as well as baud-rate and pulse-width validation on the received data.

A noise filtering mechanism is implemented to enhance the receiver robustness and improve bit decoding. The received ARINC 32-bit word is checked for correct decoding and label matching (based on the Control Register). Invalid ARINC words or words which do not meet the necessary matching are ignored and are not loaded into the FIFO.

Each ARINC429IP-RX core contains a Programmable Labels Table which stores up to 256 labels for label recognition. If label-compare is enabled (in the control register), the Rx Core will store in its FIFO only words which passed label matching to the labels in the Table.

Specific control lines are used to reset and program labels in the Labels Table.

Advanced Verification

To ensure a fully reliable and robust product the core was developed using an advanced verification environment that includes a Random-Generation engine, Code-Coverage and assertion tools.

All ARINC429 functions and performance requirements were verified.

Simple Integration

In order to simplify the integration of the core, a sample VHDL design that uses the core is provided, including:

comprehensive user’s manual.

- VHDL gate level model of the core for the target technology.

- Transceiver VHDL model that connects the core with 2 buses.

- bus tester VHDL model that generates ARINC 429 messages and checks the return replies.

- top Test bench that instantiates all of these components to a working example.

- simulation script for compiling and running the core.

DO-254 Certification

The ARINC429IP IP Core can be certified with DO-254 DAL-A through DAL-E. Along with the IP, Sital provides a testing environment and a set of documents, which the user is required to present to the certification authorities