Integrated 1553

Integration development platform of MIL-STD-1553 applications for Xilinx platforms

Sital’s “Integrated 1553” solution can save you a full year of unnecessary long MIL-STD-1553 integration !

Prototyping designs like 1553B/1760 I/O are challenging due to the lack of standard interfaces solution and good hardware/software integration.

As a result, this often leads to long integration times involving electrical, PCB and software design teams exposing the project to unnecessary risks and delays and sometimes loosing projects to competition,

For instance those who wish focus on their core competence and value add, Sital provides the “Integrated 1553″ as a turnkey end to end solution for 1553B/1760 application and prototype development.

Get your 1553B/1760 channel up and running and start writing application code within 30 minutes!

The Result – “Integrated 1553” packs everything needed to get your MIL-STD-1553 interface off the ground so you can focus on what you do best !

When the time comes to further develop the prototype into a product,

all of our “Integrated 1553” internal components are made available for production licensing at competitive prices ensuring design integrity and SWaP-C compliance.

You can find us on Xilinx also – link

“Integrated 1553” – PACKAGE CONTENT:

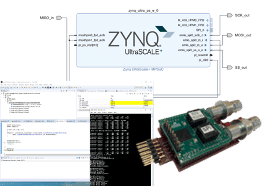

- BRD1553XVR-P – 1553B/1760 daughter board with PMOD interface (to Hosting Board) and front end triax connectors . Includes 1553B/1760 transceivers and transformers.

- BRM1553D – MIL-STD-1553B/1760 FPGA IP Core, pre configured to support the AXI bus architecture back-end and the PMOD front-end.

- Device Drivers – Low latency AXI bus device drivers to control the BRM1553D FPGA IP , support for stand alone (No-OS) or PetaLinux environments

- API – DDC compatible API , written in ANSI C, fully verified and tested.

- Sample Application – Skeleton ANSI C applications for BC/RT/MT use cases , providing a walkthrough of how the API is leveraged to a working flow for all types of application modes.

- VIVADO Project Files – Xilinx VIVADO IDE project files for a rapid deployment on Xilinx designs.

- Test Scripts – Out of the box testing and validation scripts for the FPGA IP to make sure it is loaded correctly and it’s pinout is fully functional.

- Documentation – Fully documented user manual, quick start guide, HSID and software source code.

SUPPORTED XILINX FPGA FAMILIES:

- Ultrascale+, Virtex

SUPPORTED FPGA IP Cores:

- BRM1553D – BC/RT/MT IP Core for MIL-STD-1553/1760

- BRM1553D-CS – BRM1553D version with real-time cyber security monitoring and anomaly detection

- BRM1553D-SnS – BRM1553D version with real-time cyber security monitoring and circuit fault location detection