# MIL-STD-1553 & PP194 or H009 Bus Tester & Analyzer Hardware Software Interface & User's Manual

# **MultiComBox**

Bus Tester & Error injections Multiple RT & Word Monitor 4 ports of RS422/485

29 July 2015 – Injected data now for simulated RTs only

20 Jan 2016 – added Sital Smart Wiring block

8 Nov 2016 – updated to version 9.0 with Cyber Attack Emulation – see register 4B

25 Jan 2017 – Added RS485 Tx tail measure for detection of missing termination

March 2018 – Read and write of time tag counter

www.sitaltech.com

The information provided in this User's Guide is believed to be accurate; however, no responsibility is assumed by Sital Technology for its use, and no license or rights are granted by implication or otherwise in connection therewith. Specifications are subject to change without notice.

© All rights reserved. No part of this User's Guide may be reproduced or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of Sital Technology.

#### **Table of Contents**

| Introduction                                                                                  |    |

|-----------------------------------------------------------------------------------------------|----|

| Block Diagram                                                                                 | 6  |

| 16PP194 extension                                                                             |    |

| PP194 MultiRIU stand-alone mode                                                               |    |

| The data transmitted at that time is the same data that was sent on the Tx bus at Data time 3 |    |

| Physical Bus assignments                                                                      | 8  |

| Memory space                                                                                  | 9  |

| BC tester interface                                                                           | 10 |

| MultiRT Modes                                                                                 |    |

| BC\Multi RT mode                                                                              |    |

| MultiRT standalone mode                                                                       | 10 |

| Word Monitor interface                                                                        | 11 |

| Data Payload source                                                                           | 12 |

| H009 message format                                                                           | 14 |

| RS422/485 Uart                                                                                | 15 |

| Sital Smart Wiring Block                                                                      | 16 |

| Asynchronous message mode                                                                     | 16 |

| Programming and Setup                                                                         | 18 |

| Memory Structure                                                                              | 19 |

| Registers 0x30 to 0x34                                                                        |    |

| Stack                                                                                         |    |

| Message State                                                                                 | 25 |

| Data Block                                                                                    |    |

| Memory Setup Example                                                                          | 28 |

| Registers                                                                                     |    |

| Async Message Block                                                                           |    |

| Read only registers                                                                           |    |

| 48 bit Time Tag Registers Address 0x00100x0012                                                |    |

| General Status Register Address 0x0020                                                        |    |

| Frame Time Remaining Register Address 0x0021                                                  | 34 |

| Frame Number Register Address 0x0022                                                          | 34 |

| Time Tag LSB Register Address 0x0024                                                          | 35 |

| Time Tag LSB Register Address 0x0025                                                          | 35 |

| Bus Load Register Address 0x0026                                                              | 36 |

| Word Monitor Address 0x0028                                                                   |    |

| Temperature Sensor address 0x0029                                                             |    |

| RS485 tail length 0x002A                                                                      |    |

| RS422 Line-in 0 status address 0x002D                                                         |    |

| RS422 Line-in 1 status address 0x002E                                                         |    |

| Version Register Address 0x002F                                                               |    |

| Write only registers                                                                          |    |

| RS422 Line 0 configuration Register Address 0x0040                                            |    |

| RS422 Line 1 configuration Register Address 0x0042                                            |    |

| RS422 Line 0 frequency divider register Address 0x0041                                        |    |

| RS422 Line 1 frequency divider register Address 0x0043                                        |    |

| Error Definition 0x0044                                                                       |    |

| Error Params 1 0x0045                                                                         |    |

| Sync Pattern 0x0046                                                                           |    |

| Multi RIU Simulation enable Register Address 0x0047                                           |    |

| User Port 0x0048                                                                              |    |

| Interrupt enable Register Address 0x0049                                                      |    |

| Configuration Register Address 0x004A                                                         |    |

| Configuration Register 2 Address 0x00 HAB                                                     |    |

| Reset & Stop Register Address 0x004C                                                          |    |

| Frame Time Register Address 0x004D                                                            |    |

|                                                                                               |    |

| Multi RT 0 to 15 enable Register Address 0x004E         |    |

|---------------------------------------------------------|----|

| Multi RT 16 to 30 enable Register Address 0x004F        |    |

| Supported Message Formats                               |    |

| Word Monitor Memory Contents                            | 49 |

| The Data Symbol                                         |    |

| The Time Symbol                                         |    |

| PP194 words organization in Word Monitor                |    |

| H009 words organization in Word Monitor                 | 53 |

| Appendix A: Gap/Rate mode                               | 54 |

| Definition.                                             |    |

| Existing sequencing mechanisms.                         | 54 |

| Sital Technology's enhanced BC Sequencing               |    |

| Appendix B: Sample memory setup                         |    |

| Example 1 – used in VHDL simulation testing             |    |

| Example 2 – This is the memory setup used by SW ver 1.3 |    |

| Example 3 – 64 messages memory usage                    |    |

| Example 4 – Maximum memory usage                        |    |

| Appendix C: MultiComBox MultiRT standalone              |    |

| Appendix D: User Code modes                             |    |

| Appendix E: RS422/485 working flow                      |    |

| Appendix F: EBR1553 mode                                |    |

| Appendix F: pTDR1553 memory                             |    |

| Appendix G: Cyber Attack Mode                           |    |

|                                                         |    |

## Introduction

The TestersChoice bus tester is a compact design that is intended for MIL-STD-1553B (1553) and 16PP194 (194) bus testing of Line Replacement Units (LRUs) that communicate over standard 194 and 1553 busses.

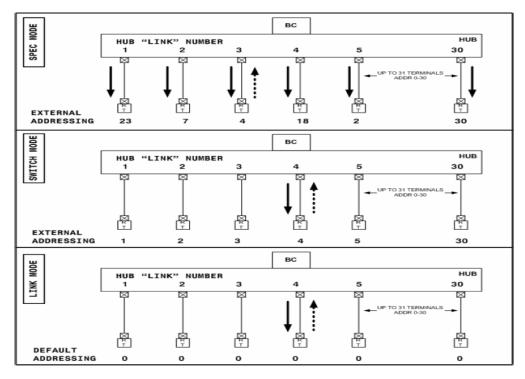

The TestersChoice incorporates a Bus Controller (BC) in addition to simulating Multiple Remote Terminals (Multi RT) or Simulate Multiple RTs as a stand-alone mode.

Multi RT is required for testers to simulate those RTs that exist in the simulated system. The Multi RT can simulate 0 to 31 RTs based on user programming.

A unique Live-RT mode changes all RTs that are not simulated to Live RTs. Live RTs reply to the TestersChoice transmit commands with data payload that changes over time. All receive commands are replied with status words according to the standard.

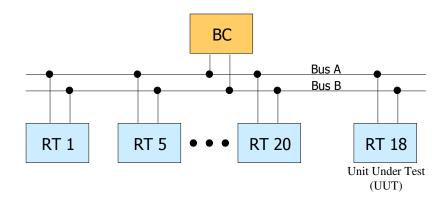

A typical operational system would look like:

To-Be-Simulated system block Diagram

Single Bus Controller with multiple Remote Terminals

#### **Block Diagram**

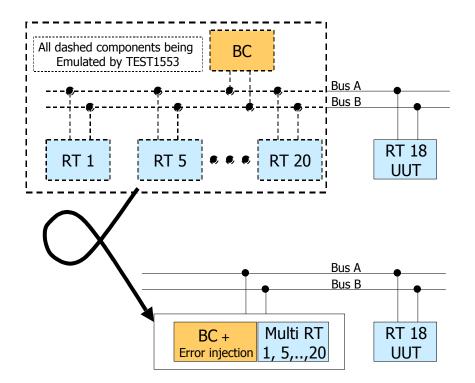

When building a simulation environment for the Unit Under Test (UUT), and assuming that the Interconnect Control Document (ICD) includes communications between the RTs themselves, a tester would need to simulate both the BC and all of the RTs that communicate with the UUT RT.

The same system in simulation would thus look like in the following diagram:

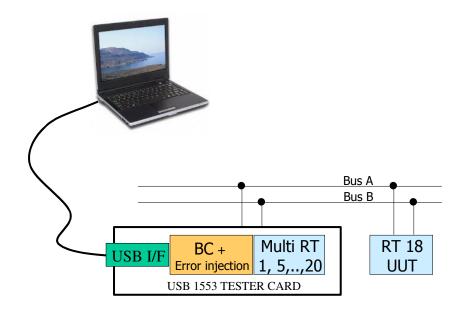

The TestersChoice design can be incorporated in a tester card. The tester card is being controlled by software in a host computer. PCI, USB among other communication means can serve as the connection between the tester card and the host PC. Typically, the card is supplied with SW drivers. The SW driver relieves the programmer from the need to master the memory and register mapping that the BC and Multi RT need for their continuous operation.

The TestersChoice design also incorporates a word monitor. This word monitor is like a 1553 scope, allowing the host a good view of what words ran on the bus. The word Monitor Monitors everything including words sent by TestersChoice.

A block diagram that includes a sample USB interface and the host computer can be found in the following block diagram.

USB card example

#### 16PP194 extension

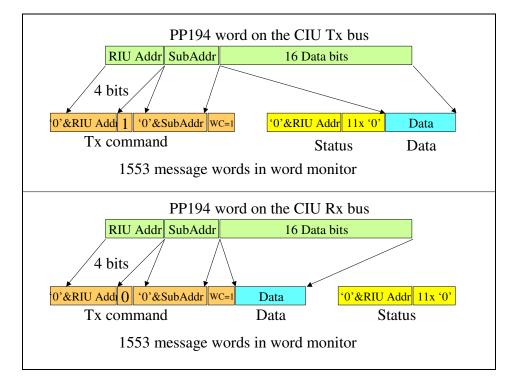

The PP194 standard is a weapon bus used on F16s. The PP194 standard uses the same physical level electric characteristics as the 1553 standard. The protocol is different. The PP194 bus is built of twice the number of wires as the 1553 bus. There is the Tx bus, which output from the CIU (BC of PP194) and the Rx bus, which is input to CIU and output from the RIUs (RTs). The RIUs reply on the Rx bus and listen to the Tx bus. There is full redundancy with a backup bus.

In latest F16s, MIL-STD-1553, or better MIL-STD-1760 (Weapons version of 1553), has been added on the 194 Rx bus. This was done to allow the usage of advanced weapons needing more data than provided by the older PP194 standard.

This creates a unique situation that two different communication standards share the same physical media and do not disturb each other. It also challenges the ability of the Stores system to manage a bus with two concurrent message formats in the same frame.

TestersChoice was designed to operate as a BC with each message being tagged as PP194 or 1553. The word monitor also supports 1553 and PP194.

#### PP194 MultiRIU stand-alone mode

In MultiRIU mode (User code 2) the MultiComBox can only specify data time 4 status word on the Rx bus.

The data transmitted at that time is the same data that was sent on the Tx bus at Data time 3.

#### Physical Bus assignments

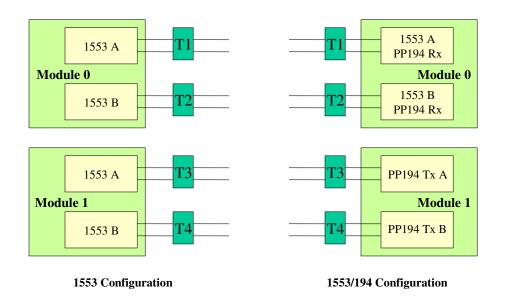

TestersChoice supports two modules each with a single full duplex 1553 bus (4 twisted pair lines). These two 1553 modules support a single 194 bus. Module 0 is the Rx bus and its backup, and Module 1 accommodates the Tx bus.

TestersChoice in the 1553/194 configuration would work as in 1553 mode, i.e., two busses in two modules. If one of the frame messages is defined as a 194 message (see Message Control bit 2) it will use both modules. The Data or Go/NoGo command will be transmitted on module 1 (T3 and T4), and the data echo or status will be transmitted on module 0. All 1553 messages in the frame would be transmitted on module 0 (T1 and T2).

#### Memory space

The full 64Kx16 bit memory is arranged in blocks of 8K by 16 bits blocks.

| Size | range               | Usage                                                                                           |

|------|---------------------|-------------------------------------------------------------------------------------------------|

| 8K   | 0x0000 to<br>0x1FFF | Module 0 1553 / PP194 / H009 bus tester or MultiRT.                                             |

| 8K   | 0x2000 to<br>0x3FFF | Module 0 1553 / PP194 word monitor. In card from version 6: the memory is external and 256Kx16. |

| 8K   | 0x4000 to<br>0x5FFF | Module 1 1553 / PP194 / H009 bus tester or MultiRT.                                             |

| 8K   | 0x6000 to<br>0x7FFF | Module 1 1553 / PP194 word monitor. In card from version 6: the memory is external and 256Kx16. |

| 256  | 0x8000 to<br>0x80FF | Module 0 - Sital Smart Wiring block - see appendix F                                            |

| 8K   | 0x8100 to<br>0x9FFF | Future use.                                                                                     |

| 1K   | 0xA000 to<br>0xA3FF | Module 0 RS422 line 0 transmit                                                                  |

| 1K   | 0xA800 to<br>0xABFF | Module 0 RS422 line 0 receive                                                                   |

| 1K   | 0xB000 to<br>0xB3FF | Module 0 RS422 line 1 transmit                                                                  |

| 1K   | 0xB800 to<br>0xBBFF | Module 0 RS422 line 1 receive                                                                   |

| 8k   | 0xC000 to<br>0xDFFF | Future use.                                                                                     |

| 1K   | 0xE000 to<br>0xE3FF | Module 1 RS422 line 0 transmit                                                                  |

| 1K   | 0xE800 to<br>0xEBFF | Module 1 RS422 line 0 receive                                                                   |

| 1K   | 0xF000 to<br>0xF3FF | Module 1 RS422 line 1 transmit                                                                  |

| 1K   | 0xF800 to<br>0xFBFF | Module 1 RS422 line 1 receive                                                                   |

#### **BC tester interface**

The Host interfaces with the BC by updating a shared memory and a set of registers. The TestersChoice works with the clock frequency that is used by the host thus the update is being done with a HW synchronous method eliminating the chance of partial update of memory or registers. The memory and register structure and contents is defined in the following sections.

#### MultiRT Modes

TestersChoice has two modes of operation for the MultiRT. One is BC\MultiRT, and the other is MultiRT standalone, or simply MultiRT. For the MultiRT standalone, please refer to applicable section. Following is a description for the BC\MultiRT where the BC state engine can also simulate RTs that are not physically attached to the bus.

#### BC\Multi RT mode

The only definition required for the Multi RT is a 31 bit long register that enables the relevant RTs. If the Host sets bit X of this register high, TestersChoice will simulate this RT. If this bit is set low, Multi RT will not respond to commands sent to that RT. Valid values for X is 0 to 30. For simulated RTs transmitting data, the BC message block should be loaded with the data words and status words that the simulated RT will transmit, as explained in the following sections. For simulated RTs receiving a message, the message block will be loaded with the data and status words that the simulated RT received.

RT to RT (RT2RT) transactions are supported by the TestersChoice. Both the transmitting and-or the receiving RTs, can be simulated.

Bit (RT) 31 represents the broadcast address in 1553 standard. If a broadcast command issued by the BC, the Multi RT will not perform any special action since Broadcast does not require any RT response. Therefore, when bit 31 (BCST address) of that register is set high, Live RT mode is enabled. No real RTs should be connected to the tester in this mode. All NON-Simulated RTs become Live RTs. Live RTs' transmitted payload increments over time and is used to verify proper system operation when operating in stand alone without real RTs connected.

For PP194 there are up to 15 RIUs, and a reset RIU (0). A vector of simulated RIUs should be similarly supplied for the RIU simulation.

#### MultiRT standalone mode

This mode is used when a BC exists on the bus outside TestersChoice, and TestersChoice is required to reply to its commands for several RTs.

This mode of operation is designed to act with as much similarity in SW control as the BC\MultiRT mode.

To enter this mode, it is required to set the User Code option to 2 (bit 1 set high, other bits don't care). After mode 2 is set, the HW responds differently to SW commands, especially BC Go command will not initiate transmission, but rather enable the MultiRT standalone state machine to start replying to bus commands.

For this mode, the SW loads a stack of commands and a 31-bit register that defines which RTs are to be simulated.

When a command is detected on the bus, the MultiRT state machine checks if the RT referred by the command is enabled for simulation. If it is not, the state machine will continue to monitor the message but will not do anything else.

If it is to be simulated, the MultiRT state machine scans all of the "BC" stack entries for the length defined by stack length, for a machine command. If found, the MultiRT state machine starts replying to the message with the status words and data words pointed by the stack entry. This allows the SW to setup the data and status contents that the simulated RT is required to reply.

If the scanning for the command fails, but the RT has to be simulated, the MultiRT will reply to the command with clear status (only RT address set) and with data words with value picked up from address 0 to 0x20 of the shared memory (preset to all zeros).

In real time systems, the SW would want to replace the data on every frame. This capability exists in TestersChoice. Each time a successful scan yielded a stack entry, the time tag is updated for the time the message was detected. The SW reads the stack and data blocks when the frame is completed. If it detected that the Time changed from the previous frame read, it should assume the message was executed (data sent ort received).

The BC\MultiRT SW control algorithm initiates a BC Go command, and monitors the activity of the BC state machine. After the active part of the frame finishes (bus list transmission completed) a passive state is entered. During the passive state, the SW normally exchanges data with the HW to read the received data and to load the stack and data for next frame. In the MultiRT standalone mode, the BC Go does not initiate the active part, but rather enables the MultiRT state machine. MultiRT will not reply to any message until instructed by BC Go. Since the BC Go isn't synchronized with the external BC, the HW automatically guesses frame passive time after both busses are inactive (passive) for a period of 1 ms. It is assumed that a external BC does not embed 1 ms message gap before it completes its bus list transmission. Once the MultiRT detected passive time, and the number of frames to Go is finished, the MultiRT state machine will go offline until a new BC Go command even if there are additional messages on the bus. As with the BC\MultiRT mode, once in the passive time, and the SW initiates a BC Go, the HW emulates Active time for the SW until the first bus activity, and from this time on, the actual activity monitor will report bus status to the SW.

If User Code 0022 is issued, the MultiRT will reply with illegal message (rather than not reply at all as in User Code 0002) for commands sent to an enabled RT but the command could not be located in the message list of the frame. This ME bit in status word will be replied when the MultiRT state machine is running!

If User Code bit 7 is set in MRT mode, i.e., 00A2 or 0082, then the Word Count field is ignored when searching for messages.

#### **Word Monitor interface**

The word monitor is a tool embedded inside the TestersChoice that monitors both 1553 lines and records all 1553 words that exist on them.

Each 1553 word is tagged by a tag word that provides additional data on the 16-bit data word. The tag word information includes the sync type, any error, the gap from the previous word and channel.

Notice the word monitor is not a message monitor, so message assembly has to be done by software if needed.

There are 4K words (8K bytes) mapped for the Word monitor (\*see upgrade of card type B). These 4K words are mapped after the 4K words that serve the TestersChoice BC + MultiRT circuits.

The Word Monitor provides a single address pointer, that point to the next location that a word will be written to. The first address is 0x2000. The highest address is 0x3FFF. The address counter will cyclically return to 0x2000 after 0x3FFF.

The software should record the address pointer, wait for the transactions, then read the new address pointer, and finally read all words between the two pointers.

For pp194 each 24 bit word is stored in two consecutive entries, first the header 8 bits as LSBs with its descriptor, and then the 16 payload bits with its descriptor.

For cards of type B, there is an external memory added to save longer recording periods that the host PC is busy.

Since version 6.1 of the HW, the address pointer value is also between 0x2000 and 0x3FFF (0x6000 and 0x7FFF for module 1) but the 12 LSBs represent the number of 32 word blocks of data. In case the SW reads a value of 0x2001, it should assume that at least 32 words have been recorded and ready for download via the USB. In other words, the actual word address is derived from the 12 LSBs of the HW pointer times 32.

In case the incoming data stopped before completing a 32 word block, the HW would wait for 1 ms before injecting 32 words of time stamp in to the buffer.

For SW simplicity, the above HW pointer functionality would be the same for Card Type A and Card Type B.

#### **Data Payload source**

As of Version 7.2 of the tester the data automatic hardware incremental method was changed.

Bit 31 (MSB of the 32 bit vector that defines which RT is simulated) define the data source for the messages.

If this bit is '0', then the data transmitted in the message is loaded from the software. If this bit is '1' the data that is sent on the lines is sourced from a 16-bit register that constantly increments for each new data word.

Injecting incremental data from the hardware allows for hardware autonomous operation and data generation for BER test. It can increment with no PC load in 100% bus activity frames.

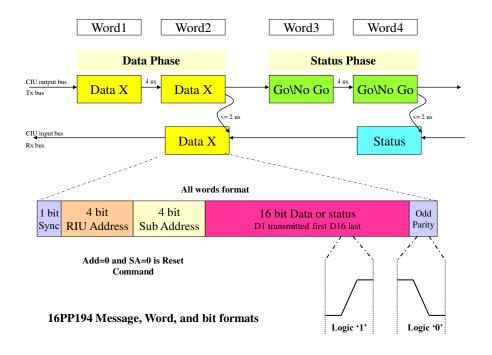

#### **PP194 message format**

The PP194 message is a very simple 6 word message performed in two phases. The first phase is the data phase.

The second phase is the Go/NoGo phase, or status phase.

In each phase the CIU issues a 26 bit long word, and the RIU replies to that word after exactly 2 us, in parallel to the CIU transmitting that first word again. The CIU decides if to perform the second Go\NoGo phase pending a success in the first phase.

In any case if something goes wrong, the CIU can send a reset command.

In the Data phase, the CIU sends a 26 bits data. The RIU digest the data and echoes the same data word back after 2 us.

If this phase is successful, when a Go\NoGo word of 26 bits is received by the RIU, it replies after 2 us with the status word in parallel to the CIU sending the Go\NoGo again.

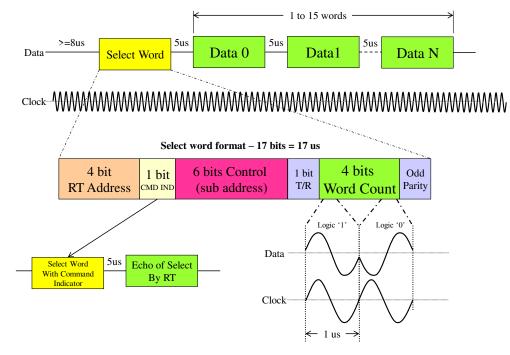

#### H009 message format

The H009 messages include BC to RT and RT to BC without status, as well as mode commands with one data word.

The standard calls for clock and data signals for each bus A or bus B. Total of 4 lanes per bus compared with 2 lanes per bus in 1553.

The command word is composed of 17 bits, and has at least 8 us of bus idle preceding it. Each data word is preceded by 5 us bus idle.

There is no full handshake with status respond.

The command word bits are:

| Unit Addr 4 | CMD IND 1 | Control 6 | T/R | #Words 4 | Parity 1 |

|-------------|-----------|-----------|-----|----------|----------|

Unit Address is a 4 bit field that indicates which unit is targeted for this message. Command indication is a single bit. When high it indicates it's a mode command with one word. Control is like the sub-address in 1553 and covers 64 different values using 6 bits. T/R is high for a unit transmit message and low for a unit receive message. Number of Words has 4 bits to specify 0 to 15 words. 0 is not used as far as we know. Odd Parity of 1 bit terminates each H009 word.

H009 Message, Word, and bit formats each bus A or B

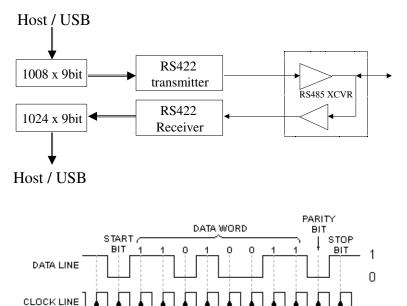

#### RS422/485 Uart

The MultiComBox incorporates 2 transceivers of RS422/485 for each of the modules.

There are a total of 4 bi-directional RS422/485 lines.

Each transceiver includes a transmitter and a receiver.

The receiver also receives every word transmitted.

There is a 1008 word buffer for each one of the transmit buffers, and 1024 words for the receive buffers, total of 4 buffers for transmit, and 4 buffers for receive.

Each one of the words can be 5 to 9 bits long and also include a parity bit if needed.

The bit rate or baud rate can be set for each line. In addition, the parity type and stop bits can be set separately for each one of the lines.

The last 16 words of each transmit buffer is dedicated for control registers.

tib ytiraP htiw drow ti8

The reception of all transmitted words allows for wrap around testing as well as working in both full duplex and half duplex protocols.

For full duplex, it is possible to connect line 0 as a transmit bus, and line 1 as a receive bus. For half duplex it is possible to transmit a number of words to the remote unit, and that remote unit replies on the same lines. The receive buffer will contain the transmitted words followed by the received words.

For these modes, an additional setup has to be defined. Line mode can be transmit, or transmit\receive.

When Line mode is set to transmit, the RS422 hardware buffer will always drive the line, even when not transmitting.

When Line mode is set to transmit\receive, the buffer is driven only when transmitting. Please refer to the appropriate registers description and Appendix E for Software control of the channels.

#### Sital Smart Wiring Block

The Passive TDR block for MIL-STD-1553 is designed to monitor the bus constantly and provide TDR information on all active UUTs on the bus, including the UUT in which it is located. The block works throughout the mission, and picks up wiring faults, and latches the relevant information required to determine that there is a fault, and where on the bus.

Refer to "pTDR1553 Hardware Software Manual.docx" for additional information.

#### Asynchronous message mode

As of March 20<sup>th</sup> 2018 a new Async message sending mode was added to the transmission capabilities of MCX BC.

This new mode of operation allows the controller to inject a new message instantaneously to the transmissions on the bus.

- 1. If the MCX is running and transmitting a bus list, say message #3, and the Async is initiated, then it will be transmitted ONCE after #3 ends, but before message #4.

- 2. If MCX is running, but it is in a passive phase, i.e., between two frames, the message would go out instantly with no delay, and the first message on the next frame might be delayed until the Async message has been transmitted.

- 3. If the MCX is in idle mode, i.e. no bus lists are running, the Async message would be instantly transmitted ONCE and MCX returns to idle mode.

- 4. If the MCX is in idle mode, i.e. no bus lists are running, the Async message would be instantly transmitted ONCE and if during transmission, bus-list transmission is engaged, MCX would start the bus-list transmission back-to-back with the Async message completion.

Some avionic systems make use of asynchronous messages, and the above method facilitates this mode to MCX.

The usage of Async message on IDLE simplifies the procedure for sending messages, and avoids using bus lists. The controller can transmit any message one after the other, and each can be different from the previous one. This mode of operation might be useful for some application that want the controller intimately managing the bus list. Please note that if message results are tested, there would be no bus activity periods between two messages, depending on this result analysis takes.

An Async message is defined by a standard message block format, but one which resides between address 0 and 7. Writing word 7 initiates the transmission.

A second Async 2 message is provided in addresses 8..F. Using these two async messages, one can work in pipe line mode, and achieve very high bus utilization even if using USB interface.

It is recommended that the data blocks and state blocks be located after the last block. Assuming there are 64 blocks supported, block location 65 and 66 should be used.

#### **RT** response times

As of April 2018, MCX can control the RT response time in mRT mode (and later in BC + mRT) to a programmed time.

Before, the response time was set to 8 us. This is the default time.

The control is by specifying a value between 1 and 511. Each step, i.e. the LSB is a clock cycle of the main clock. The main clock can be one of 30-Mhz (MCX), 32-Mhz (GRIP2) and 33-Mhz (PCI), and potentially others. The value of the

Register address 0x18 serves as the programming port, and reporting port for the global setting of RT response time.

Please note that the counter starts counting from the end of the command so that a value of 1 can create a continuous, no gap mode. Some monitors might see that as a fault. The standard allows 4 us to 14 us, and these are between the zero crossings of the parity to the zero crossing of the sync. There is still  $\frac{1}{2}$  us after that parity sync, and  $\frac{1}{2}$  us sync before zero crossing, so there are actually 2 us to 12 us bus "dead" time expected if the command has no leftovers on the bus.

The RT Response time counter starts counting from the end of the parity, and once reached the programmed value, would start the sync. So it actually counts the bus "dead" time. Setting it to 2 us, would make a 4 us response, and 2 us bus "dead" time.

The mRT is designed initially to avoid response if the bus is not quite ("dead" bus) when it is time to transmit the response. If the response time is set to very fast, it might be needed to respond before the bus does quite down. In order to persuade the mRT to respond on a busy bus, an additional bit should be set to '1' in the register.

It was measured that the bus dead time is about 660 ns if counter is set to 0.

| I muxc    |          | Z              |     |       |         |          |       |         |                                       |            |         |        |       |         |         |       |               |     |

|-----------|----------|----------------|-----|-------|---------|----------|-------|---------|---------------------------------------|------------|---------|--------|-------|---------|---------|-------|---------------|-----|

| 🔶 muxd    |          | Z              | L   | 1     | · · · · |          |       |         | · · · · · · · · · · · · · · · · · · · | <b>s</b> ' | ···.    |        |       |         |         |       |               |     |

| 🔶 muxa    |          | Z              |     |       |         |          |       |         |                                       |            |         |        |       |         |         |       |               |     |

| 🔶 muxb    |          | Z              |     |       |         | 5        |       |         |                                       |            |         |        |       |         |         |       | ···· <u>.</u> | L   |

| 🛛 🖅 🕂 🕞 🖪 |          | 0841           | 084 | 1     |         |          |       |         |                                       |            |         | 222    | 2     |         |         |       |               |     |

|           | ise_time | 7A00           | 7A0 | 0     |         |          |       |         |                                       |            |         |        |       |         |         |       |               |     |

|           |          |                |     | · · · | <br>    |          | · · · | - · · · |                                       |            |         |        |       |         |         | · · · |               |     |

|           |          | 480,964,094 ps |     |       | 300,000 | 0,000 ps |       |         | 304,000                               | ,000 ps    |         |        | · ·   | 308,000 | ,000 ps |       |               | 312 |

| 📄 🦢 🦢     | Cursor 1 | 305,864,434 ps |     |       |         |          |       |         |                                       |            | 305,864 | ,434 p | 669   | ,972 ps |         |       |               |     |

| ê 🖉 🤤     | Cursor 2 | 306,534,406 ps |     |       |         |          |       |         |                                       |            | 3       | 06,534 | 4,406 | ps      |         |       |               |     |

Kindly refer to register 0x18 description in the following sections.

# **Programming and Setup**

#### **Overall Structure**

There are number of configuration and setup registers that are mapped on the memory space. These registers are written both into the memory and registers, and read from the registers if these registers are being updated by the core, or from the memory when they are constant for the HW.

The memory and registers are arranged in groups. The belonging of a particular data to each group depends on the owner of the data. If the Host PC writes to a particular register of memory, then it is the owner of the data. If the TestersChoice core writes / updates it then the core is the owner of that data.

All registers owned by the same owner are mapped consecutively inside a group, thus the Host PC can read or write them with burst operations rather than accessing particular registers and bits and performing single word read or write operations. This technology increases the communication efficiency between the Host PC and TestersChoice.

The memory mapping was designed to use pointers to data structures. A careful assignment of these pointers by the SW allows for configuring large chunks of data to the same groups yielding bigger bursts of read and write cycles.

#### **Operation Methodology**

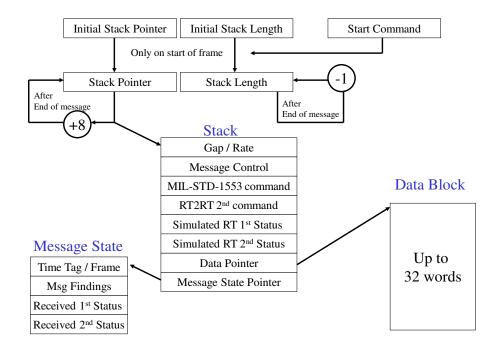

The basic operation methodology is for the Host PC to setup a list of message entries in a stack structure. Each stack entry defines a particular message that would be transmitted on the bus. The Host defines an initial stack pointer and an initial stack length and issues a start command. Once started, the core starts transmitting the messages one after the other until all messages have been transmitted. When finished, the core will wait for the frame time counter to zero. If the mode of operation is auto-repeat mode, a new frame would begin at this point, else the core will remain idle.

Several frames can be arranged in the memory structure with the initial stack pointer and initial stack length set to point to the relevant frame before the start command.

#### **Notation**

If a reference is made to a particular register and a specific bit the notation is R01B12 for Register 01 bit 12.

If a reference is made to a particular memory location the notation is M0100 for memory address 0x100.

#### **Memory Structure**

The host should prepare the frames of messages in the memory stack prior to initiating the start command.

Stack entries point to memory data blocks and Message state block described in the following sections.

Please refer to the following memory structure:

In PP194 mode, the message is mapped on the same memory structure. The Hardware will activate the command in PP194 mode automatically.

The following PP194 highlights are:

- 1. Where not mentioned, stay the same as in 1553.

- 2. Message Control a single bit #2, if set enables a PP194 message.

- 3. MIL-STD-1553 command 4 bits of RT address, and 4 bits of Sub address will be used. All other bits are ignored.

- 4. RT2RT 2<sup>nd</sup> command ignored.

- 5. Simulated RT 1<sup>st</sup> Status If the RIU (RT) is simulated, the transmitted status word will be taken from this entry.

- 6. Simulated RT 2<sup>nd</sup> Status Not used in PP194 mode.

- Data pointer Points to the data block. The first data in the block is the PP194 data word contents used in data phase (word 1 and word 2). The second word is the Go or NoGo code used in status phase (word 3 and word 4).

- 8. Msg findings used. Reports errors in message.

- 9. Received 1<sup>st</sup> Status contains the status return in status phase.

- 10. Received 2<sup>nd</sup> Status not use in PP194.

#### Registers 0x30 to 0x34

**Initial Stack Pointer** (Fix address 0x0030) – The Host PC loads this address. The Address points to the first stack entry message of the frame. Any address with 3 LSBs being '0' and higher or equal to 0x0048 can be used. Notice that several frames of messages can be stored in the memory structure prior to the start command, and just before the start command the Host PC loads this pointer to the frame it wants.

The value of this register is copied to the running stack pointer and is not used by the core until start of next frame. The host PC can update this parameter 1 us after issuing the start command for the next frame.

**Initial Stack Length** (Fix address 0x0031) – The Host PC loads this address. This parameter indicates the number of messages that would be processed in the next frame. The value of this register is copied to the running stack length and is not used by the core until start of next frame.

If 0 is loaded to this parameter, no messages would be transmitted after start command. The host PC can update this parameter 1 us after issuing the start command for the next frame.

**Stack Pointer** (Fix address 0x0032) – The core loads this address. The Address points to base of the current stack entry message being processed. The value is incremented by 8 following the end of each message processed.

The Host PC should not write to this register AFTER start command and BEFORE the frame is complete.

**Stack Length** (Fix address 0x0033) – The core updates this address. The value of this parameter indicates the number of stack entries that are still going to be processed. This parameter is decremented by 1 after each message. When zeroed, frame transmission stops. The Host PC can write to this register but the core will overwrite the value after each message completion.

**Start Command** (Fix address 0x0034) – By writing to the start command address, the TestersChoice machines start processing the messages. The value written to the start address is the number of frames will be executed. The value read from this register is the value written to it. The core does not change its value. A frame number up counter can be read from register 0x22.

Writing to this register should be the last write before frame begins.

Writing the value 65535 will transmit 65535 frames. : Writing the value 1 will transmit one frame. Writing the value 0 will transmit endlessly.

#### Stack

The stack is a set of message entries, 8 words deep each. Each stack entry is composed of 8 words. The stack is arranged with indirect pointing database. The stack is intended to be written only once during setup by the host, then to be used by the core during operation.

A stack pointer points to one of the messages. The initial stack pointer is loaded by the host, and could point to any non reserved location in the 64Kx16 memory space, however, initial stack pointer should point to a word address with all of three LSBs being zero (Word address 0x0050 should be the base address for stack).

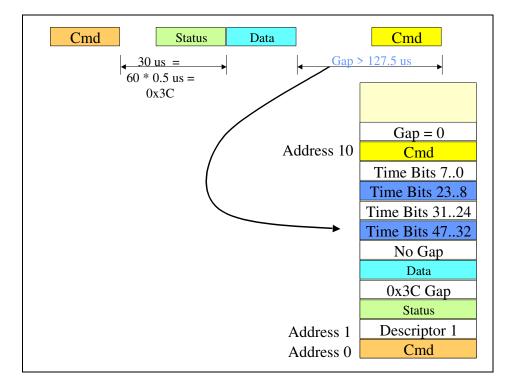

**Gap / Rate** (stack offset 0) - This parameter works in either one of two modes of operations: the message Rate mode, or the message Gap mode. The mode is controlled globally for all stack entries by a configuration register.

#### Gap mode

In Message Gap mode, this register defines the amount of microseconds from the beginning of this message to the beginning of the next message. A value could be in the range of 0 us to 64K us =  $\sim$  65 ms.

A value shorter than the message actual length on the bus results with a default intermessage gap of about 10 us.

In cases where not all messages are needed in every frame, but rather some are transmitted every other frame, or every 4<sup>th</sup> frame... for example, it is popular to define minor and major frames. With the usage of these delays, the host can program minor and major frames.

The HW core however, supports a more compact and efficient method for sequencing of such low rate messages. The Rate mode is a much more appropriate method for such systems.

#### Rate mode

For each message define its rate. Possible rates are

- 0 skip this message.

- 1/1 send every frame.

- 1/2 send every second frame.

- 1/4 send every forth frame.

- 1/8 send every  $8^{th}$  frame.

- :

1/N – Where N is a power of 2 and  $N_{max}$  = 2^14, i.e., once every 16,384 frames.

15 – send only once. Core will change to 0 after transmission.

If two stack entries point to the same message, than the resulting rate of that message would be higher. The resulting rate would be the sum of both rates. For example 1/4 + 1/16 would be 5/16, which is almost 1/3 of the frame rate.

The HW core sequences the messages at lower rates, such that for each frame, only the 1/1 rate messages are transmitted along side only ONE slower rate messages. Such that 1/N (N>1) messages and 1/M (M>1, N<>M) messages are not transmitted in the same frame.

The HW core provides a register that indicates the frame number. After start command this frame counter starts counting up until the operation is stopped. The host can determine which message is transmitted on which frame using a simple equation. This will allow the host to update the transmitted data buffers on time.

It might happen that the transmission length in time of all messages of rate 1/1 and messages of lower rate in a specific frame sum up to a total length which is too long for the frame length. If one of the following frames is not crowded, the HW core supports message

skew definition. A specific stack entry message can be skewed forward 1 to 15 frames ahead from its designated frame.

Please refer to Appendix A for a more in-depth theoretical description of Gap and Rate modes.

**Message Control** (stack offset 1) - This parameter defines the various modes of operations for the specific message. Each bit is explained below.

The "Write Verify" mode allows the SW to instruct the HW to perform a Verify before write operation on the received data words. If the RT message words are known expected data "Write Verify" mode can be enabled. In this mode words written into the memory are first verified against the memory location contents where they are written, and if the data does not match, the "good data block received" bit 3 in the message state register is reset.

**MIL-STD-1553 command** (stack offset 2) - This parameter defines the 1553 command that will be transmitted for this stack entry.

**RT2RT 2<sup>nd</sup> command** (stack offset 3) – In case the Message control define this message as an RT to RT format, This parameter defines the 2<sup>nd</sup> 1553 (Transmit) command that will be transmitted for this stack entry.

**Simulated RT 1**<sup>st</sup> **status** (stack offset 4) – In case the command approaches an RT that is defined as a simulated RT, This status word would be transmitted by TestersChoice as if an RT transmitted it. If it's a receive or transmit command, TestersChoice will use this status word. If this command is an RT2RT command format, then this status word would be the status of the first simulated RT. If both RTs are simulated, then this will be the transmitter's status. If only the receiver RT is simulated, this status would be its status word. For simplicity of programming, if only one RT is simulated, fill both this entry and the next with the same "returned" status.

**Simulated RT 2<sup>nd</sup> status** (stack offset 5) – only in RT2RT command format, with BOTH RTs simulated, this parameter would be the receiver RT status word.

**Data Pointer** (stack offset 6) – This word can point to any 64Kx16 memory location. This pointer points to the data block in memory. Data block should be 1 to 32 words deep. It would be efficient to arrange all transmitted data blocks consecutively in memory to allow their update with a single burst write. If misfortune happens and this parameter is un-initialized or is zero, data will be stored in the first 32 locations which is reserved just for such misfortunes...

Many data pointers can point to the same location (if these messages' data is irrelevant for the Host PC).

**Message State Pointer** (stack offset 7) – This word can point to any 64Kx16 memory location. This pointer points to the Message State Block, which collects message information during its transmission.

**Bit description of stack contents:** Notice first word (offset 0) has two options depending on configuration.

| Offset | Purpose                                           | Bits | Description                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------|---------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | Inter-message<br>gap<br>( <mark>Gap mode</mark> ) | 150  | Number of microseconds between the start of this message and start of next message.                                                                                                                                                                                                                                                                                                                          |

| 0      | Spacing<br>( <mark>Rate mode</mark> )             | 158  | Spacing gap: Number of microseconds between <b>end</b> of message and <b>start</b> of next message. Could be left zero.                                                                                                                                                                                                                                                                                      |

|        | Rate<br>( <mark>Rate mode</mark> )                | 74   | <ul> <li>Case N (decimal value of bits) is</li> <li>0: Skip this message.</li> <li>1: transmit this message every frame.</li> <li>214: transmit this message every 2^(N-1) frames.<br/>Will be transmitted in frames who's frame N-1<br/>LSBs = 2^(N-2) (unless skewed).</li> <li>15: Transmit this message once. The HW core resets this value<br/>to 0 after message has been transmitted once.</li> </ul> |

|        | Skew<br>( <mark>Rate mode</mark> )                | 30   | Frame skew: Defines a number M between 0 and 15. Will skew<br>the message M frames away from its rate planned location<br>(defined above).<br>M is derived from max(N-1,4) bits of this 4 bit field.<br>Example: If N is 3 then only bits 10 are added to "10" (2) and<br>compared to 3 LSBs of frame number.                                                                                                |

| 1      | Message<br>Control<br>Deafult:<br>xFA80           | 15   | Transmit internal time tag data in Synchronize with data mode<br>command:<br>'1' - Use time tag counter as data.<br>'0' - Use data word in message block.<br>In PP194 – conditional Go/NoGo –<br>'1' will transmit the Go/NoGo command if data phase OK.<br>'0' will transmit Go/NoGo phase regardless of data phase.                                                                                        |

|        |                                                   | 14   | <ul> <li>'1' – Mask Message Error (ME) bit in status word.</li> <li>'0' – No masking. If ME is set, this will cause "Status Bit Set" condition.</li> </ul>                                                                                                                                                                                                                                                   |

|        |                                                   | 13   | <ul> <li>`1' – Mask Service Request (SR) bit in status word.</li> <li>`0' – No masking. If SR is set, this will cause "Status Bit Set" condition.</li> </ul>                                                                                                                                                                                                                                                 |

|        |                                                   | 12   | <ul> <li>`1' – Mask busy bit in status word.</li> <li>`0' – No masking. If busy is set, this will cause "Status Bit Set" condition.</li> </ul>                                                                                                                                                                                                                                                               |

|        |                                                   | 11   | <ul> <li>'1' – Mask Sub-System Flag (SSF) bit in status word.</li> <li>'0' – No masking. If SSF is set, this will cause "Status Bit Set" condition.</li> </ul>                                                                                                                                                                                                                                               |

|        |                                                   | 10   | <ul> <li>'1' – Mask Terminal Flag (TF) bit in status word.</li> <li>'0' – No masking. If TF is set, this will cause "Status Bit Set" condition.</li> </ul>                                                                                                                                                                                                                                                   |

|        |                                                   | 9    | '1' – Mask Reserve bits (RSRV) in status word.                                                                                                                                                                                                                                                                                                                                                               |

|   |                                        | 1   |                                                                                                                                                                                                                                                                                                             |

|---|----------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                                        |     | '0' – No masking. If RSRV is set, this will cause "Status Bit Set" condition.                                                                                                                                                                                                                               |

|   |                                        | 8   | '1' – Retry enable. Perform retry if message fails. The number of retries and the retry bus is defined in configuration register in address 0x004A.                                                                                                                                                         |

|   |                                        | 7   | <ul> <li>`1' – Transmit on bus A.</li> <li>`0' – Transmit on bus B.</li> </ul>                                                                                                                                                                                                                              |

|   |                                        | 6   | '1' – Perform internal loop back test. Message does not go out<br>to 1553 bus but rather loop backed just like the normal echo of<br>the transceiver. The TestersChoice core simulates the RTs, thus<br>this internal loop back can be completed with out any error.                                        |

|   |                                        | 5   | If R08B11='1', i.e., Mask mode for BCST bit then this bit is the<br>mask bit:<br>'1' - will mask checking BCST bit<br>'0' - will verify BCST is not '1', otherwise "Status Set"<br>condition found.<br>ELSE in compare mode:<br>This bit should be equal to BCST bit, else "Status Set"<br>condition found. |

|   |                                        | 4   | '1' – End OF Message Interrupt Enable (if not masked by interrupt mask register).                                                                                                                                                                                                                           |

|   |                                        | 3   | <ul> <li>'1' – "Write Verify". Before Writing received data to memory, verify it matches the memory preloaded to the data block. Only for transmit commands.</li> <li>Check Message state bit 4 to see if verify passed.</li> <li>'0' – do not verity. (Receive commands are not verified).</li> </ul>      |

|   |                                        | 2   | '0' – 1553 message format.<br>'1' – PP194 message format.                                                                                                                                                                                                                                                   |

|   |                                        | 1   | Ignored. Should be '0' for future compatibility.                                                                                                                                                                                                                                                            |

|   |                                        | 0   | '1' – The message is an RT2RT command format.                                                                                                                                                                                                                                                               |

| 2 | 1553 command                           | 150 | The 16 bits of the command sent.<br>The core detects BCST and Mode formats automatically.<br>PP194 – Use 4 bits of Address and Subaddress only.                                                                                                                                                             |

| 3 | 2 <sup>nd</sup> command                | 150 | In RT2RT mode only: this is the transmit command.<br>The RT2RT mode set in the message control word bit 0.<br>PP194: not used.                                                                                                                                                                              |

| 4 | 1 <sup>st</sup> Simulated<br>RT Status | 150 | This entry defines the first RT simulated status response.<br>This data will be transmitted by TestersChoice.<br>PP194: simulated status word.                                                                                                                                                              |

| 5 | 2 <sup>nd</sup> Simulated<br>RT Status | 150 | This entry defines the second RT simulated status response in RT2RT format. This data will be transmitted by TestersChoice. Not used in PP194.                                                                                                                                                              |

| 6 | Data Block<br>Pointer                  | 150 | Points to the data block where the message data is either stored or read from.                                                                                                                                                                                                                              |

| 7 | Message State<br>Pointer               | 150 | Points to the starting memory location of the Message State block.                                                                                                                                                                                                                                          |

#### Message State

The message state block incorporates 4 words that are collected from the bus while the message is being processed.

**Time Tag / Frame** (block offset 0) – This parameter works in either one of two modes of operations: the message Rate mode, or the message Gap mode. The mode is controlled globally for all stack entries by a configuration register.

<u>In Gap mode</u> - The 16 LSBs of the 32 bit time tag counter are stored here when the message was launched by the core.

<u>In Rate mode</u> – A frame counter is incremented by 1 at EOF. This frame counter value is stored in this entry when the message is transmitted.

**Message Findings** (block Offset 1) – This register is collects a number of parameters during the message processing. Bits 13 downto 0 are updated at EOM after change.

**Received RT 1<sup>st</sup> status** (block offset 2) – The first status that was received from a real non-simulated RT is stored here.

**Simulated RT 2<sup>nd</sup> status** (stack offset 3) – only in RT2RT command format, the second status (Rx Status) that was received from a real non-simulated RT is stored here.

|   | Name                            | Bit | Description                                                      |

|---|---------------------------------|-----|------------------------------------------------------------------|

| 0 | Time Tag Word 16                | 150 | 16 LSBs of the real time counter. Written by core when the       |

|   | LSBs. ( <mark>Gap mode</mark> ) |     | message started.                                                 |

| 0 | Frame Number                    | 150 | Frame number when this message was transmitted. Frame            |

|   | ( <mark>Rate mode</mark> )      |     | number is incremented every EOF.                                 |

|   |                                 |     | It is recommended to init this value to 0xFFFF before run.       |

| 1 | Message findings                | 15  | End Of Message – Set to $1'$ by the core when the message has    |

|   |                                 |     | been complete.                                                   |

|   |                                 | 14  | Start Of Message - Set to '1' by the core when the message has   |

|   |                                 |     | been started.                                                    |

|   |                                 |     | In most cases, this bit is stuck at '1' after end of message if  |

|   |                                 |     | there is a 1553 bus-coupling problem.                            |

|   |                                 | 13  | '0' – Was sent on Bus A.                                         |

|   |                                 |     | `1' – Was sent on Bus B.                                         |

|   |                                 | 12  | 1' – Error was found in the message.                             |

|   |                                 |     | Bits 10, 9, 8, 3, 2, 1, 0 indicate cause of error.               |

|   |                                 | 11  | Status Set. One of the status bits (excluding BCST bit) of the   |

|   |                                 |     | status return was `1'. Masking ignored.                          |

|   |                                 |     | BCST bit works in either mask mode or compare mode.              |

|   |                                 |     | In mask mode it works like other mask bits on the BCST bit.      |

|   |                                 |     | In compare mode, Status set occurs if BCST bit is different from |

|   |                                 |     | bit 5 of BC control word.                                        |

|   |                                 | 10  | Format Error. The returned echo from the RT contained 1553       |

|   |                                 |     | violations. See bits 3, 2, 1, 0 for a more accurate guess of the |

|   |                                 |     | source of the problem.                                           |

A detailed description of the Message State block:

|   | 1                               |      |                                                                                                                                                                                                                                                                                                                                                                                 |

|---|---------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                                 | 9    | Response timeout. The RT responded too late or didn't respond                                                                                                                                                                                                                                                                                                                   |

|   |                                 |      | at all.                                                                                                                                                                                                                                                                                                                                                                         |

|   |                                 |      | In PP194 – The RIU did not respond properly.                                                                                                                                                                                                                                                                                                                                    |

|   |                                 | 8    | Loop back failed. The nature of 1553 bus is that every word transmitted, is also echoed back. The core verifies that the echo is correct and equal to the transmitted word. If not, this bit is set to '1'. Also set in messages with error injected. Tip: The source of this type of error could be transceiver fault, or bus coupling problem.<br>In PP194 –Loop back Failed. |

|   |                                 | 7    | Unmasked Status bit set. This bit will be set to '1' if one of the status bits are set high and its appropriate mask bit in the BC control word is unmasked ('0'). BCST bit influences only in mask mode. See registers section for description of BCST bit.                                                                                                                    |

|   |                                 | 65   | Number of retries done for this message. "11" is 3, "10" is 2                                                                                                                                                                                                                                                                                                                   |

|   |                                 | 4    | Good data block received by TestersChoice, waiting in Data<br>Block.<br>'1' – after an RT-BC, RT2RT, and Transmit Mode code with data                                                                                                                                                                                                                                           |

|   |                                 |      | commands if the message ended OK.<br>'0' – after other message types, or if the above type of                                                                                                                                                                                                                                                                                   |

|   |                                 |      | message was invalid.                                                                                                                                                                                                                                                                                                                                                            |

|   |                                 |      | '0' – for received words that did not match the expected values if "Write Verify" mode is enabled for the message.                                                                                                                                                                                                                                                              |

|   |                                 |      | Loop back test failure does not cripple this bit result.                                                                                                                                                                                                                                                                                                                        |

|   |                                 |      | In PP194 – Both phases completed successfully and a real RIU sent its status and saved to memory.                                                                                                                                                                                                                                                                               |

|   |                                 | 3    | '1' indicates the RT responded with wrong RT address.                                                                                                                                                                                                                                                                                                                           |

|   |                                 | 2    | In PP194 – RIU status respond with wrong RIU address.<br>'1' indicates that the RT transmitted a wrong number of words.                                                                                                                                                                                                                                                         |

|   |                                 | 2    | In PP194 – RIU Data phase error.                                                                                                                                                                                                                                                                                                                                                |

|   |                                 | 1    | <ul> <li>'1' – Incorrect sync type response by RT.</li> <li>In PP194 – RIU Status phase error.</li> </ul>                                                                                                                                                                                                                                                                       |

|   |                                 | 0    | 1' – Invalid word. Indicates that the RT responded with a word containing 1553 errors.                                                                                                                                                                                                                                                                                          |

|   |                                 |      | In PP194 – The RIU responded with Manchester / parity error.                                                                                                                                                                                                                                                                                                                    |

| 2 | Received 1 <sup>st</sup> status | 150  | First status received from un-simulated RT.                                                                                                                                                                                                                                                                                                                                     |

|   | Dessived 2nd -t-t               | 15.0 | In PP194 – Status bits of status word.                                                                                                                                                                                                                                                                                                                                          |

| 3 | Received 2 <sup>nd</sup> status | 150  | Second status received from un-simulated RT.                                                                                                                                                                                                                                                                                                                                    |

#### Data Block

The data block is the location for either storing data words received from the bus as a response for transmit commands, or as a location for the Host PC to write data word payloads that need be transmitted to the bus.

Two different messages can point to the same data block. New data will override the former.

### Memory Setup Example

Typical Memory structure for a two-message design:

| Hex Address  | Description                         | Comments                              |  |  |

|--------------|-------------------------------------|---------------------------------------|--|--|

| 0000 to 0007 | Async 1 Message block               | Asynchronous message insertion        |  |  |

| 0008 to 000F | Async 2 Message block               | Asynchronous message insertion        |  |  |

| 0010 to 0013 | Real Time Counter                   | Read and write real time timer        |  |  |

| 0018 to 001F | Reserved Memory                     | Intended for future usage.            |  |  |

| 0020 to 002F | Card State Registers                | Initialized by host.                  |  |  |

| 0030         | Initial Stack Pointer               | Initialized by host.                  |  |  |

| 0031         | Initial Stack Length                | Initialized by host.                  |  |  |

| 0032         | Current Stack                       | Updated by HW                         |  |  |

| 0033         | Stack Remaining                     | Updated by HW                         |  |  |

| 0034         | START command                       | Initialized by host.                  |  |  |

| 0040 to 004F | Configuration Registers             | Initialized by host, updated by core. |  |  |

| 0050         | Gap / Rate                          | Initialized by host.                  |  |  |

| 0051         | Message Control                     | Initialized by host.                  |  |  |

| 0052         | 1553 command                        | Initialized by host.                  |  |  |

| 0053         | RT2RT 2 <sup>nd</sup> command       | Initialized by host.                  |  |  |

| 0054         | Simulated RT 1 <sup>st</sup> status | Initialized by host for simulated RT. |  |  |

| 0055         | Simulated RT 2 <sup>nd</sup> status | Initialized by host for simulated RT. |  |  |

| 0056         | data pointer                        | Initialized by host.                  |  |  |

| 0057         | State pointer                       | Initialized by host.                  |  |  |

|              |                                     |                                       |  |  |

| 0058         | Gap / Rate 🔪 🔪                      | Initialized by host.                  |  |  |

| 0059         | Message Control \                   | Initialized by host.                  |  |  |

| 005A         | 1553 command                        | Initialized by host.                  |  |  |

| 005B         | RT2RT 2 <sup>nd</sup> command       | Initialized by host.                  |  |  |

| 005C         | Simulated RT 1 <sup>st</sup> status | Initialized by host for simulated RT. |  |  |

| 005D         | Simulated RT 2 <sup>nd</sup> status | Initialized by host for simulated RT. |  |  |

| 005E         | data pointer /                      | Initialized by host.                  |  |  |

| 005F         | State pointer /                     | Initialized by host.                  |  |  |

|              |                                     |                                       |  |  |

| 0100         | Frame number /                      | Last transmitted frame /              |  |  |

|              | Time Tag 16 LSBs                    | Last transmitted time                 |  |  |

| 0101         | Message Findings                    | HW reports message state & errors     |  |  |

| 0102         | Received 1 <sup>st</sup> status     | Received for non-simulated RT.        |  |  |

| 0403         | Received 2 <sup>nd</sup> status     | Received for non-simulated RT.        |  |  |

|              |                                     |                                       |  |  |

| 0104         | Frame number /                      | Last transmitted frame /              |  |  |

|              | Time Tag 16 LSBs                    | Last transmitted time                 |  |  |

| 0105         | Message Findings                    | HW reports message state & errors     |  |  |

| 0106         | Received 1 <sup>st</sup> status     | Received for non-simulated RT.        |  |  |

| 0107         | Received 2 <sup>nd</sup> status     | Received for non-simulated RT.        |  |  |

|              |                                     |                                       |  |  |

| 0108 - 0127  | 1 <sup>st</sup> message block       |                                       |  |  |

| 0128 – 0147  | 2 <sup>nd</sup> message block       |                                       |  |  |

#### Memory Setup before start