# MIL-STD-1553 High Reliability IP Core for FPGAs

For 1553 BC, RT, MT – Space & High Reliability Implementations

# Compact, Robust, Reliable MIL-STD-IP-Cores

# More IP Cores from Sital:

- MIL-STD-1553 IP Core DDC\* enhanced mini-ACE\* interface

- MIL-STD-1553 Transceiver and Transformer

- MIL-STD-1553 Testers and Boards

- MIL-STD-1553 Design Services

# **Key Features and Benefits**

- Mil-Std-1553 Intellectual Property for FPGAs

- Suitable for any Hign-Reliability MIL-STD-1553 BC, RT, MT implementation

- Very small FPGA area utilization

- Supports any even clock frequency

- Two possible interfaces available:

- Front-End for simple implementations, does not require CPU for management, no SW required.

- DDC® Compatible for more complex applications

- Provided with full verification environment

- Passed full validation testing by 3rd party

- Based on vendor and technology independent VHDL code

Designed from ground up for use in space, Sital's BRM1553ERL IP core, offers uniquely compact, robust and reliable BC, RT, MT solutions for any FPGA and ASIC device. The core implements special means for overcoming problems related to radiation and harsh conditions often found in space applications.

The core implements means like Hamming-Code, watch-dog timers and pure logic, to reset all state-machines on every new 1553 message.

Selected by NASA to be used in satellites and space-crafts, BRM1553ERL ensures a successful and robust implementation of Mil-Std-1553 in any space and high-reliability application.

More information available at **www.sitaltech.com**

# Specifications

# Compatibility

- MIL-STD-1553B Notice 2

- RT Validated according to test plan from MIL-HDBK-1553A

- 1Mbps Data Rate

- Connects to any transceiver-transformer pair

# **FPGA Requirements**

- 10 pins to connect to transceiver

- Standard FPGA pads

- Area usage with accordance to configuration

- Dual-Port Memory can be selected by the user

# Clock

• Any even frequency from 12MHz and up, selected by the user

# **Supported FPGAs**

- Any FPGA with sufficient number of LUTs

- FPGA families from the following vendors:

- o Actel

- Aeroflex

- o Xilinx

- o Altera

- o Lattice

- o QuickLogic

\* For other FPGAs or ASIC please consult Sital

# **BRM1553ERL Deliverables**

- EDIF net list for the core for FPGA family, memory and clock frequency

- User's manual

- Sample VHDL code that incorporates the core

- Synthesis script for sample code

# **Available Configurations**

- BRM1553ERL-RT: Remote Terminal

- BRM1553ERL-BC: Bus Controller only

- BRM1553ERL-MT: Bus Monitor

- · Any combination of the above

- Simple Front-End or DDC®

Compatible Back-end Interface

#### Sital Technology Ltd.

Tel: +972-9-7633300 Fax: +972-9-7663394

Email: info@sitaltech.com Web: www.sitaltech.com

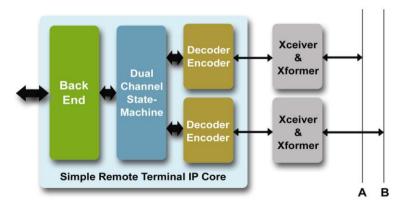

# A Core for Simple or Complex Implementations

In its Simple Front-End configuration, the BRM1553ERL IP Core is suitable for small and simple Mil-Std-1553 implementations, where no CPU is present or required or where relatively short messages are sent over the bus. The core is particularly useful in applications of protocol translators, and where small amount of messages are sent and received.

As a DDC® Compatible, the core incorporates a backend logic that arranges the messages in a predefined memory structure, which simplifies the interface between the 1553 bus and the local CPU. The BRM1553ERL core can act as a full replacement for DDC<sup>®</sup> enhanced mini-Ace<sup>®</sup> devices as the data is arranged in the same way.

#### **Small Gate Count**

Sital's MIL-STD-1553 IP cores require very small space from FPGA. The following table shows examples of the area usage of an RT, in different FPGA devices:

|         |                      | Area Usage (4-LUT count) |                                          |

|---------|----------------------|--------------------------|------------------------------------------|

| Vendor  | Product Family       | Simple Front-End         | DDC <sup>®</sup> Compatible<br>Interface |

| Actel   | RTAX-S               | 1036 Modules             | 3950                                     |

| Xilinx  | Virtex-II, Spartan 3 | 805                      | 3360                                     |

| Altera  | Stratix, Cyclone 3   | 930                      | 3550                                     |

| Lattice | LatticeXP            | 764                      | 3100                                     |

- These numbers are approximate. Other FPGA vendors and families are available

- Actual area usage may vary according to core configuration.

#### **Manchester Decoder**

The unique Manchester decoder can work with any even clock frequency from 12Mhz and up to reduce clock sources and clock domains on board (reduces EMI/RFI).

Advanced algorithms for filtering out noise and disturbances enable the core to operate in harsh environments.

# **State Machine Recovery**

The RT1553ERL implements means such as Hamming-Code, Watch-Dog timers and pure logic, in order to prevent the state-machines from locking or go into unknown states.

The core can recover from any 'X' states injected by simulation, whenever a new message is detected on the bus.

### 3<sup>rd</sup> Party Validation

The RT1553ERL IP Core successfully passed the full MIL-STD-1553B Notice 2 RT Validation test, according to a test plan from MIL-HDBK-1553A. Validation tests were performed by an independent 3rd party laboratory.

# **Advanced Verification**

BRM1553ERL

To ensure a fully reliable and robust product the core was developed using an advanced verification environment that includes a Random-Generation engine, Code-Coverage and assertion tools. All MIL-STD-1553B functions and performance requirements are verified.

#### **Simple Integration**

In order to simplify the integration of the core, a sample VHDL design that uses the core is provided, including:

- A comprehensive user's manual.

- A VHDL gate level model of the core for the target technology.

- A Transceiver VHDL model that connects the core with 2 buses.

- A bus tester VHDL model that generates 1553 messages and checks the return replies.

- A top Test bench that instantiates all of these components to a working example.

- A simulation script for compiling and running the core.

# **About Sital Technology**

Founded in 1993, Sital Technology is a leading provider of IP cores and products for Mil-Std-1553.

SITAL Technology's key quality resource is its creative, talented and professional staff. Our engineers are veterans of the Israeli Air Force, who served in the technical units of the F-16 avionics systems. They gained knowledge and experience with the MIL-STD-1553 standard from the bottom up, both as design engineers for MIL-STD-1553 components and as technicians working on the aircrafts.

Among our many customers you can find NASA, ESA, Thales, Orbital Science Corp., Elbit, Rafael, Israeli Aerospace Industries (IAI), Astronautics, Israeli Ministry of Defense, Elta, Honeywell, BAE Systems and many others.

\* Products and company names listed are trademarks or trade names of their respective companies.