# Mil-Std-1553 IP Cores -

# A Short Introduction to an Emerging Technology

Ву

# Ofer Hofman and Duli Yariv

# Sital Technology Ltd.

September 2006

© All rights reserved

# The Old Days

Mil-Std-1553 was released in August 1973, and was first used in the F-16 fighter plane. Back then, a full 1553 Bus Controller (BC) + Remote Terminal (RT) design spread across 3 cards filled up with military grade TTL family components (54LSXX). The design was usually based on micro code for control and state-of-the-art logic for designing the 1553 decoder.

In the '80s, ICs (integrated Circuits) for 1553 decoder encoder emerged, and 1553 was reduced to a single card with less TTL devices and higher complexity ICs dedicated to specific functions.

At the beginning of the `90s, companies started to develop

Gate Array ASICs (Architecture Specific ICs) and got a single chip that would handle the entire digital portion of the 1553 card. On the other hand, the analogue transceiver was also condensed from discrete devices into a single module, usually metal case and quite big.

The next step was for specialized companies such as DDC, Aeroflex NHI and others, to integrate the digital and the analogue parts into a single module and later on to a single mixed signal chip.

These single mixed signal ICs take bigger parts of the market in the last few years.

The last emerging technology in 1553 is the availability of MIL-STD-1553 IP (Intellectual Properties) cores. The IP cores integrate with other user logic into an FPGA (Field Programmable Gate Array). The FPGAs can be programmed to perform any digital circuit by means of loading the net-list of components into them. In most recent cards, FPGAs serve many tasks and are widespread.

The IP cores solution thus incorporates a part of an FPGA and an analogue transceiver.

# Why to Use IP Cores

## Advantages of IP Cores

There are a few reasons to prefer an IP core over an off the shelf 1553 ICs:

#### **Eliminate Problems Related to Single Source**

Unfortunately, the current situation is that all of the suppliers of 1553 ICs have their unique interface and functionality. This fact makes it hard, or practically impossible to change provider of 1553 ICs, because it would require a re-design of card and software.

It also makes the fabrication of 1553 cards to be locked to a single vendor of 1553 ICs, which may create difficulties such as low availability, delays in deliveries, high pricing, etc.

An IP core does not suffer from this problem. Once the IP core is licensed to a customer, there is no supply chain involved. The customer integrates the IP core in the form of EDIF net-list into the FPGA, and therefore there are no delays in production.

FPGAs also provide full flexibility in designing different interfaces and features into the IP Core, so that the customer can select a different vendor of 1553 IP Core and continue to use the same interface and features.

### Small Footprint

Assuming an FPGA already exists on the card for other tasks, adding an IP core to it does not require any additional ICs on the card. The IP core might consume 2 to 15% of a common FPGA, thus would not impact its size. All that is needed on the card is the analogue transceiver interfacing with the FPGA. The analogue transceiver is much smaller than a dedicated 1553 IC, and has less number of pins.

Smaller footprint also contributes to extending the MTBF (Mean Time Between Failures) thus improving reliability.

#### **Lower Price**

Assuming the FPGA exists anyway, the price per 1553 node, now comprises only of the analogue transceiver and the IP core use-license. Since there are many suppliers for analogue transceiver, its price is competitive, and along with the use-license can deliver more than 50% reduction in 1553 node price for moderate quantities.

IP use-license price is more flexible than an IC prices since ICs combines both the IP assets of the IC producer and costs of manufacturing, shipping and stocking. Since these ICs are digital + analogue mixed signal ICs, their NRE (Non-Recurring Expense) costs are much higher than digital ICs.

### Flexibility

Once a 1553 IC is soldered to the card, this card is limited to the 1553 functions of that IC. With an IP core, the 1553 can be enhanced, modified, or replaced by other IP cores. For example, if the card serves as an RT (Remote Terminal) in one project, it can be reused in another project as a BC (Bus Controller) by simply changing the FPGA load file.

Due to integration and reduction of size for example, a single box can do the work of two RTs. An IP core can be thus upgraded to a multi-RT core instead of a single RT core. Area of core in the FPGA would rise from 5 % to 7%... This is impossible with an IC.

An even more extreme example would be to change the 1553 IP function with a different protocol that uses the same 1553 transceivers, such as PP194 (F16 stores bus), or monitor H009 bus (F15 bus), or ARINC 708 (Weather RADAR data).

A supplier of an Avionic product containing a 1553 node would want to target its product to as many air planes and avionic systems as possible. When developing the 1553 node on a card and placing a 1553 IC, the supplier nails himself to those systems that were tested, no commitment to proper functionality in untested systems. IP core is flexible. If a new requirement arises in a future system, the core could be enhanced to meet these new requirements in a number of weeks, or in some cases – even days, compared with the need to replace the 1553 IC and the design of the card.

The IP core can be targeted for many FPGA technologies and Vendors to produce a net-list.

The IP core net-list can be generated and supplied for many FPGA technologies.

## **Easy Evaluation**

IP cores samples can be supplied within a couple of hours from the time a customer expressed his interest in the core. These samples could be a limited version of the core such that it would perform 95% of the functions required of the core. The customer can check simulations, integrate the limited IP core, and test its behavior in lab. No commitment is needed from the customer, and no money exchange is required for the supply of the limited net-list.

### Pricing

IP cores are delivered as net-lists for an FPGA. These are computer files. No hardware is needed to exchange hands when delivering the IP core.

1553 ICs have to be fabricated, stocked and shipped. Fabrication and shipping costs are minimum price for the ICs. So IP cores and ICs start their pricing from different starting points, with a great advantage to IP cores.

## **Emerging Needs**

### *Case study*: General purpose, 4 channel 1553 PMC card.

With four 1553 ICs this card is very crowded.

With a single FPGA running a PCI core, and four transceivers there is more room. Further more, if implemented in an FPGA, on each one of the channels, multiple RTs and a BC can be programmed. So this PMC card can now serve for a specific example 2 BCs and 7 RTs all located on 4 physical busses.

This type of flexibility is needed today by system providers and is only available with the use of IP cores.

## Case study: "Tails Code Key".

Sital Technology patented "Tails Code Key" technology. "Tails Code Key" is an algorithm that allows a 1553 node to pinpoint a bus problem somewhere in the bus topology. A coupler malfunction, a wire disconnects, or a connector imposes resistance, these problems hurt 1553 bus from achieving its mission. Locating these problems in an aircraft with miles of wires is a technical nightmare. "Tail Code Key" reports the distance in feet or meters where the problem is located, even if it had happened for a very short time during flight.

All BC and MT (monitor) IP cores from Sital Technology would be upgraded to include "Tails Code Key" technology.

These kinds of features are emerging as system complexity rises over time. IP cores are fit for these changes, with ICs lagging behind.

# **Requirements from IP Cores**

#### **1553 Validation**

Like any other Mil-Std-1553 devices, IP cores are not exceptional in the requirement to pass the full 1553 validation test.

#### **Support All FPGA Vendors and Families**

It is expected that IP cores would fit any FPGA vendor and family. FPGA families range between general purpose FPGAs and FPGAs with specific characteristics such as RAD-Hard, low power, non-volatile, high memory volume and a like. Customers select their FPGA device based on these characteristics and IP vendors should be able to supply net-lists for all vendors.

The VHDL source code from which the net-list is produced should be vendor independent in its code style to support all FPGA families.

#### Small Size

As discussed before, one of the advantages of IP cores over ICs is the fact that IP cores can be resided within an FPGA that performs other functions as well. Therefore the IP core must utilize small space from the FPGA.

#### Support Any Clock Frequency

Within the FPGA it is desired that there would be as less as possible clock domains. Multiple clock domains may cause overhead in FPGA design, or in some cases bad data read/write cycles. It is important, therefore, that the IP core would support a clock frequency that is already available at the card anyway, such as PCI (66MHz).

#### **Simple Integration**

Since IP cores become a part of the FPGA design, it is expected that the 1553 IP core would integrate easily into the design. That means that the core should support simple interface and be provided with all documentation along with a simulation test bench in HDL code. The supplied test bench should include a 1553 signal generator, a transceiver model for connecting as many IP cores as needed. A proper test bench simulation would involve data flow validation from the 1553 bus to the IP core, to the user code in the FPGA and back through the IP core to the 1553 bus.

#### Flexible Interface

Being a very flexible solution, IP cores can be designed to have compatible interface and functionality with existing 1553 IC. This compatibility allows for two types of IP core:

**Obsolescence replacement** – Since 1553 bus has been in use for more than 25 years, many companies provided 1553 ICs. These companies either seized to exist or discontinued their product lines. However customer products that use these ICs and are still being distributed need a replacement for these obsolescence devices. IP cores can be modified to replace these ICs. Specialized daughter boards can fit the FPGAs on the same footprint of the discontinued IC. No software or card modification is typically required from customer card.

**Second source IP cores** – No need to wait for ICs to become obsolete! IP cores can provide IC replacement for existing ICs offering the variety of advantages listed above. Sital Technology provides a 2<sup>nd</sup> source, reduced price for the popular mini-ACE IC chip by DDC<sup>1</sup>.

# Sital's 1553 IP Cores

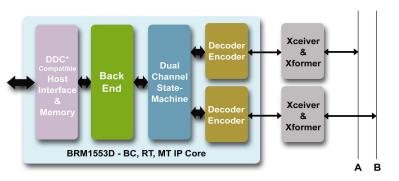

Sital's BRM1553D and RT1553FE IP Cores are suitable for any Mil-Std-1553 implementation.

The BRM1553D core incorporates a backend logic that arranges the messages in a predefined memory structure, which simplifies the interface between the 1553 bus and the local CPU. It can act as a full replacement (2nd source) for DDC enhanced mini-Ace\* devices as the data is arranged in the same way.

The RT1553FE IP Core is suitable for small

and simple Mil-Std-1553 implementations, where no CPU is present or required or where relatively short messages are sent over the bus. The core is particularly useful in space applications, obsolete replacement designs and simple applications.

The main benefits of Sital's IP cores are:

- Small FPGA area utilization

- Supports any even clock frequency

- Modular architecture allowing flexible implementations

- Provided with full verification environment

- Passed full RT validation testing by 3rd party

- Based on vendor and technology independent VHDL code

Sital also offers a design service for replacing obsolete ICs. For example, this service was practiced with a customer, who wanted to re-design an obsolete IC developed by the customer in 1991, and was out of production in 1998. Renewed orders for customer product required the development of a pin-to-pin replacement for the obsolete IC.

## Where Are Sital's IP Cores Being Used

Sital Technology's Mil-Std-1553 IP Cores are in use in several places. Please find below A short description of several projects that are using the IP cores:

<sup>1</sup> "DDC" and "mini-ACE" are registered trademark of Data Device Corporation Inc.

A company from Israel integrated the RT front-end core into an FPGA. No CPU or SW was needed. The FPGA collects a large number of discrete signals and packs them into 16 bits words for the IP core to transmit to the BC upon request. The project is running since 2004. It worked first thing, no support was requested.

NASA (USA) – Performed a long competitive analysis to select the right IP core for a general purpose 1553 RT for space missions. Target FPGA device was ACTEL Axcelerator. Actel's 1553 IP core was one of the candidates, Sital's IP core was selected.

A company from Canada, who develops avionics equipments for USAF. Used to work with DDC mini-ACE. Wanted to move to an IP core. Got an approval from USAF for using Sital's BRM1553D (mini-ACE Software compatible core). Integrated the core. Required several hours support. Working in lab to their satisfaction.

Another company from Israel, which develops defense systems. Built a PCB with room for DDC mini-ACE and a transceiver for the core. Developed the SW drivers for DDC mini-ACE. Switched from mini-ACE chip to Sital's BRM1553D (mini-ACE Software compatible core) and the core works perfect with no SW changes. Latest cards assembled did not have the DDC ICs on them any more.

An obsolete replacement project for a company who developed a 1553 ASIC in 1991 and became obsolete in 1998. All end of life purchased components finished. Pod containing the ASIC is so successful it is being sold in large numbers. The company needed a replacement for the ASIC. Sital used RT1553FE core and added glue logic to produce an RT core that performs DMA read and writes into a 80196 Intel CPU's memory. Despite the lack of documentation of the ASIC, the replacement worked perfectly in lab after 5 days of integration.